产品介绍

概述

UC6580x-00是和芯星通研制的一款支持北斗三号的双频多系统亚米级定位精度SoC。这款基于22 nm工艺的低功耗、小型化射频基带一体化SoC具有抗多径、抗干扰及高精度GNSS联合定位技术,在功耗、尺寸敏感的场景下更胜一筹。

UC6580x-00面向全球应用,拥有96个跟踪通道,支持GPS、GLONASS、北斗、Galileo、NavIC、QZSS,可多系统联合定位,并支持多种SBAS信号接收处理,向用户提供快速、准确的高性能定位体验。

UC6580x-00支持L1 + L5/L2双频单点定位及RTD,并支持AGNSS功能。可用于可穿戴、手持设备、步行导航等领域,在城市多径环境下相对于单频方案明显提升用户体验。

UC6580x-00芯片拥有车规级和工规级两种规格,参见下表。

| 型号 | 等级 | 封装 |

|---|---|---|

| UC6580A-00 | 车规级 | QFN40 |

| UC6580I-00 | 工规级 | QFN40 |

产品主要特性

基于22 nm工艺的小型化双频多系统GNSS SoC低功耗设计

兼容北斗三号的双频多系统并行捕获、跟踪技术,支持:

BDS B1I/B1C*+ B2a 或 B1I/B1C* + B2I

GPS L1 + L5 或 L1 + L2

Galileo E1 + E5a 或 E1 + E5b

GLONASS G1 或 G1+G2

QZSS L1 + L5 或 L1 + L2

SBAS L1

NAVIC L5*

实时宽窄带抗干扰技术:带内宽窄带干扰检测与移除,可抗总干扰功率不低于-75 dBm

支持L1 + L5/L2双频单点定位及亚米级RTD定位,具有优异的多径抑制算法

超高灵敏度射频与基带设计:捕获灵敏度优于-148 dBm,跟踪灵敏度优于-162 dBm

支持AGNSS

支持安全启动功能

拥有车规级和工规级两种规格,采用QFN40封装,详见章节订货信息

UC6580A-00符合AEC-Q100 Grade2

*. 特定固件版本支持。 ↩

技术指标

| 基本信息 | |||

| 通道 | 96通道 | ||

| 更新频率 | 最大10 Hz | ||

| 数据格式 | NMEA-0183,Unicore,RTCM 3.xo | ||

| 频点 | 模式一 | 模式二* | |

| BDS | B1I/B1C* + B2a | B1I/B1C* + B2I | |

| GPS | L1 + L5 | L1 + L2 | |

| Galileo | E1 + E5a | E1 + E5b | |

| GLONASS | G1 | G1 + G2 | |

| QZSS | L1 + L5 | L1 + L2 | |

| NavIC | L5* | - | |

| SBAS | L1 | L1 | |

| 观测精度 | |||

| 水平位置精度(RMS) | 单点定位:1.5 m | ||

| 垂直位置精度(RMS) | 单点定位:2.5 m | ||

| 时间精度(RMS) | 5 ns,peak-to-peak value 30 ns (24h) | ||

| 速度精度1 | 0.02 m/s | ||

| TTFF2 | |||

| 冷启动 | 26 s | ||

| 热启动 | 2 s | ||

| 重捕获 | 1 s | ||

| 灵敏度3,4 | GNSS | ||

| 冷启动 | -148 dBm | ||

| 热启动 | -156 dBm | ||

| 跟踪 | -162 dBm | ||

| 重捕获 | -159 dBm | ||

| 功耗(@25℃)5 | |||

| DCDC模式 | 捕获: 40 mA @ 3 V | 跟踪: 40 mA @ 3 V | |

| 备电模式 | 5 μA @ 3 V | ||

| 热阻(@25℃) | |||

| ThetaJA | 44.96℃/W | ||

| ThetaJB | 11.48℃/W | ||

| 工作电压 | |||

| 主电源 | 1.7 V ~ 3.6 V | ||

| IO电源 | 1.7 V ~ 3.6 V | ||

| 备电 | 1.7 V ~ 3.6 V | ||

| 通讯接口 | |||

| UARTⅹ2 | |||

| I2Cⅹ1 | |||

| SPI6ⅹ2 | |||

| 可靠性测试及认证 | |||

| 可靠性 | UC6580I-00 符合JESD47标准 | ||

| UC6580A-00符合AEC-Q100标准 | |||

| 认证 | 符合RoHS及REACH要求 | ||

o. 仅支持RTCM 3.x的消息输入。 ↩

*. 特定固件版本支持。 ↩

1. 模拟器下-33 mps直线匀速运动场景。 ↩

2. 卫星信号强度达到-130 dBm。 ↩

3. 灵敏度指标需确保CN0为41 dB,性能可能会更新 ↩

4. 外部匹配LNA以确保性能 ↩

5. 与固件版本相关 ↩

6. 当前固件暂不支持SPI接口 ↩

引脚定义

引脚分布

UC6580A-00和UC6580I-00引脚分布相同,下图以UC6580A-00为例进行介绍。

引脚说明

电源引脚说明

| 名称 | 引脚 | 类型 | 描述 |

|---|---|---|---|

| DCDC_IN | 21 | Power | DC/DC供电输入 (DCDC_IN和VDD_IO必须由同一个外部电源供电) |

| DCDC_OUT | 22 | Power | DC/DC供电输出 |

| V_CORE | 23 | Power | Core供电输入 |

| V_BACK | 6 | Power | 备份电源输入 |

| VDD_IO | 7 | Power | IO/TCXO等供电输入 (DCDC_IN和VDD_IO必须由同一个外部电源供电) |

| LDO_C | 24 | Power | Core LDO电压输出 |

| LDO_X | 2 | Power | TCXO LDO电压输出 |

| LDO_EX | 5 | Power | 仅供芯片自使用,不可对其他电路供电 |

| GND | 20 | - | 请接地 |

| V_DET1 | 8 | Power | 天线检测供电输入 |

| VDD_ANT | 9 | Power | 天线供电输出 |

| LDO_RET | 10 | Power | 备份供电输出 |

| GND | 地 |

1. 暂不支持天线检测 ↩

模拟引脚说明

| 名称 | 引脚 | 类型 | 描述 |

|---|---|---|---|

| L1_IN | 40 | RF | L1 RF输入 |

| L5_IN | 38 | RF | L5或L2 RF输入 |

| TCXO_IN | 3 | Clock | 26 MHz TCXO输入 |

| RTC_I | 12 | Clock | 32.768 kHz晶体或数字波形输入 |

| RTC_O | 11 | Clock | 32.768 kHz时钟输出 |

| NC | 4 | - | 可以悬空或接地,建议接地 |

| NC | 39 | - | NC,请悬空 |

| NC | 1 | RF | NC,请悬空 |

PIO引脚说明

| 名称 | 引脚 | 类型 | IO Reset | 描述 |

|---|---|---|---|---|

| PIO0 | 25 | IO | I/Pull-up | GPIO0 |

| PIO1 | 28 | IO | I/Pull-up | GPIO1 |

| PIO2 | 27 | IO | I/Pull-up | GPIO2 |

| PIO3 | 30 | IO | I/Pull-up | GPIO3 |

| PIO4 | 26 | IO | I/Pull-up | GPIO4 |

| PIO5 | 29 | IO | I/Pull-up | GPIO5 |

| TX | 19 | IO | I/Pull-up | GPIO6 |

| RX | 18 | IO | I/Pull-up | GPIO7 |

| SCL | 31 | IO | I/Pull-up | GPIO8 |

| SDA | 32 | IO | I/Pull-up | GPIO9 |

| D_SEL | 33 | IO | I/Pull-up | GPIO10 |

| PPS | 35 | IO | I/Pull-up | GPIO11 |

| BOOT_MODE | 34 | IO | I/Pull-up | GPIO12 |

| PIO13 | 14 | IO | I/Pull-up | GPIO13 |

| PIO14 | 13 | IO | I/Pull-up | GPIO14 |

| PIO15 | 36 | IO | I/Pull-up | GPIO15 |

| PIO16 | 37 | IO | I/Pull-up | GPIO16 |

| TMS | 16 | IO | I/Pull-up | GPIO17 |

| TCK | 15 | IO | I/Pull-up | GPIO18 |

| RESETN | 17 | IO | I/Pull-up | - |

芯片框架

芯片框图

电源管理

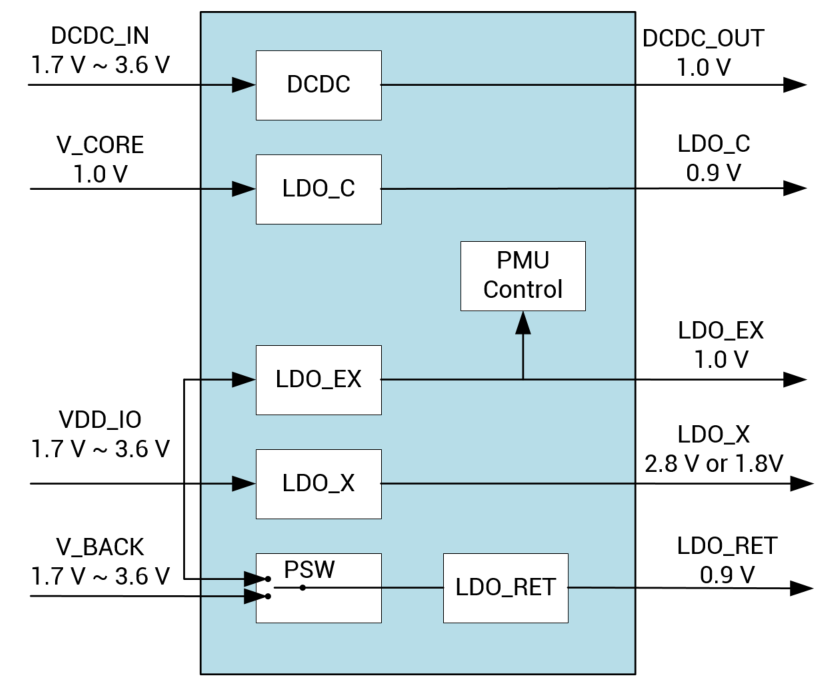

PMU提供四个电源域,由LDO内部生成并受几个电压监视器的监控。

Core电源域

Core电源域是芯片内RF和数字部分的主电源域,由V_CORE供电,V_CORE由LDO_EX或DCDC_OUT连接。后续的LDO_C转换V_CORE输入,将V_CORE转换为各自电压,并且须通过LDO_C引脚挂接去耦电容。LDO_C驱动数字逻辑部件。

IO电源域

IO电源域通过VDD_IO供电,包括芯片IO器件和片上Flash等。VDD_IO的供电电压支持1.7 V ~ 3.6 V的宽压。除了IO器件以外,PMU等设备由专用的LDO_EX供电。LDO_EX须通过LDO_EX引脚连接相应的去耦电容。

Backup电源域

Backup电源域包括RTC部分和Retention RAM。这个电源域由VDD_IO和V_BACK供电。当VDD_IO的供电电压处于正常范围时,使用VDD_IO,否则使用V_BACK。V_BACK的允许电压范围是1.7 V ~ 3.6 V。如果不需要RTC和backup功能,则V_BACK需要连接VDD_IO。

TCXO电源域

时钟电源域,给TCXO供电。该电源域有一个专用LDO称为LDO_X,也由VDD_IO供电。如果TCXO由LDO_X供电,LDO_X应连接到TCXO的电源引脚,同时用电容去耦。当然,用户也可选择除LDO_X以外的外部电源来使TCXO工作。

基于以上多电源域划分及硬件设计,UC6580x-00芯片支持以下三种功耗模式:

工作模式(Running mode):芯片各电源供电正常,CPU正常运行,各电源域供电由软件配置。所有事件,包括外部中断、通讯请求、定时等事件都可以正常处理。

备电模式(V_BACK mode):外部切断了芯片的IO供电和主供电,仅保留了V_BACK供电。此时芯片的功耗降到很低的水平,具体的功能和耗电依赖于软件对此模式的设置;上电即醒。

断电模式(Power Off mode):外部切断了芯片的所有供电,芯片完全不工作。

芯片时钟

系统需外部接入26 MHz时钟,该时钟由TCXO提供,为RF和基带PLL提供参考频率。为保证芯片启动时PLL稳定工作,需要26 MHz时钟在主电源和IO供电后10 ms内稳定工作。

系统支持RTC晶体输入,RTC晶体通常由片内的32.768 kHz振荡器驱动,该振荡器需连接外部的32.768 kHz晶体。同时系统也支持RTC时钟外部输入,输入信号幅度为0.9 V 至1.98 V,输入信号频率为32.768 kHz。两种输入方式二选一。RTC时钟频率偏差应小于20 ppm。

| 频率源 | 频率 | 备注 | |

|---|---|---|---|

| 系统时钟 | TCXO | 26 MHz | 需在主电源和IO供电后10 ms内 稳定工作 |

| RTC时钟 | 片内振荡器 | 32.768 kHz | 芯片需外接32.768 kHz晶体 |

| 片外数字波形发生器 | 32.768 kHz | 输入信号幅度为0.9 V ~ 1.98 V |

当主电源和IO供电掉电时,若V_BACK连接了备电,则基带、RF、CPU均不再工作,而RTC仍保持运行为接收机提供守时参考,该工作模式即为RTC守时模式。RTC守时模式下,Retention RAM中仍保存相关数据用作GNSS热启动。

RTC守时模式对于GNSS热启动功能为必要前提,该模式下RTC提供时间信息,Retention RAM提供星历、历书等信息。如不使用GNSS热启动功能,RTC_O需接地。在基于AGNSS的系统中,若可通过网络提供时间信息和星历作为辅助,则RTC并非必需。

| 工作模式 | 供电 | |||||

| BB | RF | CPU | RTC | Retention RAM | ||

| RTC守时模式 | V_BACK | √ | √ | |||

芯片复位

按照UC6580x-00芯片的电源结构,有两个复位域:Core域、Backup域。

Core 域有三种复位方式:

RESETN为芯片的复位引脚,当其电平为低,发出Core域复位信号,RESETN低电平持续时间应不小于5 ms。

芯片的软件系统复位信号,由固件控制。

看门狗RESET。

上述复位源中的任何一个发出Core域复位信号,则Core域将被复位。

Backup域有两种复位方式:

当V_BACK电压低于1.2 V,则触发复位。

软件控制的RTC RESET信号,由固件控制,只复位RTC计数器。

RF子系统

UC6580x-00芯片射频子系统实现了双频双通道架构,输入信号的频率范围为1166 MHz至1620 MHz。芯片接收到GNSS信号后,通过具有噪声消除技术的单端低噪声放大器(LNA)放大,然后送入射频增益模块进一步放大,从而降低了混频级的噪声系数要求。其中射频增益模块还提供单端到差分转换。在完成正交下混频转换之后,多个GNSS信号被分成两个通道。然后,分别对两个通道的I和Q信号进行低通滤波,并通过单独的可编程增益放大器(PGA)进行放大。再将两个通道的I和Q信号发送到高速ADC部分进行数据转换。

芯片射频子系统支持以下任一种模式配置:

双频L1 + L5

双频L1 + L2

L1单频多系统

LNA

LNA采用单级配置,需要外部匹配才能正常工作。建议增加外部LNA,以满足高性能要求的应用场景,外部LNA增益范围建议17 dB ~ 50 dB。在干扰复杂的环境下必需匹配外部SAW以抑制GNSS频带外的干扰。

射频增益模块

具备单端到差分转换的射频增益模块位于内部LNA后面,提供进一步放大以及从单端到差分信号的转换。

下混频器

有源正交下混频器首先将多路GNSS信号转换至中频信号,该阶段信号经下变频为两路IF信号。

中频低通滤波器

芯片内部集成I/Q低通滤波器,以滤除RF下变频后的带外噪声,提高RF系统的噪声性能。

AGC

芯片支持自动增益控制设计,收敛速度更快,计算成本更低。AGC增益控制单元依据RF系统所需的信号能量输出增益配置字,以控制射频数据链中各模块的增益配置。

PGA及ADC

芯片内部集成PGA(可编程增益放大器)及高速ADC。PGA由AGC增益控制单元配置增益值,保证RF输入信号能量在一定范围内变化时输出ADC的信号能量不变,从而保证高速ADC的输出不致饱和。高速ADC支持I/Q复采样信号输出。

基带子系统

UC6580x-00芯片提供多个接口用于数据通信或者外部设备的访问,如UART,SPI,I2C,GPIO等。

本章将从下面几个方面进行介绍:

接口

PIO复用说明

时间管理单元

看门狗

定时器计数器

接口

UART

芯片使用两个UART接口:UART1和UART2。UART均可用于与主机通信。

UART1默认情况下,PIO6/PIO7对应UART1,在标准固件版本中作为主UART。通过BOOT_MODE可将UC6580x-00芯片的通信接口映射到不同的PIO接口。PIO6/PIO7也可被用作SPI,此时没有UART1功能。关于BOOT_MODE使用及对应的通信接口映射请参见章节固件升级模式。

UART2可使用PIO15/PIO16,UART2主要用于辅助信息传输或调试。

SPI slave接口

芯片使用SPI slave接口作为与主机通信的可选方式来传输数据。同时支持由SPI slave接口加载固件。使用SPI slave的传输速率最大可支持8 Mbps,最大SPI时钟频率为8 MHz。但当SPI slave加载固件时,最大传输速率为4 Mbps。

SPI slave接口与UART1和I2C1分别复用引脚PIO6/PIO7和PIO8/PIO9,用户可在启动时使用D_SEL和BOOT_MODE来进行选择。若PIO6/PIO7/PIO8/PIO9被用作SPI slave接口,则没有UART1和I2C1功能;若PIO6/PIO7和PIO8/PIO9被分别用作UART1和I2C1,则没有SPI slave接口。

当SPI slave接口用于主机通信时,PIO14应用作SRDY(Slave Ready)信号,用于表征SPI slave是否准备就绪。

SPI master接口

芯片提供SPI master接口,可以配置PIO0/PIO1/PIO4/PIO5为SPI master功能,用于与其他SPI slave设备通信或对其进行控制。SPI master接口的传输速率最大为16 Mbps,最大SPI时钟频率为16 MHz。

默认情况下SPI master接口未启用。

I2C

芯片提供一个I2C接口(I2C1)用于固件加载及与主机进行通信。I2C1接口工作于slave模式。I2C协议和电气接口兼容100 kbps、400 kbps和3.4 Mbps。当前固件仅支持400 kbps通讯。

默认情况下,I2C1接口使用PIO8/PIO9,BOOT_MODE应在启动时处于上拉或开路状态,详情参见PIO复用说明。

I2C 时序要求

| 符号 | 参数 | 最小值 | 最大值 | 单位 |

|---|---|---|---|---|

| t_cycle | SCL时钟周期 | 100 | 3400 | kbps |

| t_high | SCL时钟高电平期间 | 0.06 | 5 | μs |

| t_low | SCL时钟低电平期间 | 0.16 | 5 | μs |

| t_su | 数据建立时间 | 0.072 | μs | |

| t_hd | 数据保持时间 | 0.072 | μs | |

| t_s_su | 起始条件的建立时间 | 0.072 | μs | |

| t_s_hd | 起始条件的保持时间 | 0.072 | μs | |

| t_p_su | 停止条件的建立时间 | 0.072 | μs | |

| t_delay | 起始条件和停止条件之间的延时 | 0.5 | μs |

串行Flash接口

串行Flash接口用于芯片与外部SPI Flash的连接。SPI Flash可用于固件存储及更新。

仅当BOOT_MODE在启动时处于上拉或开路状态时,串行Flash接口使用PIO0/PIO1/PIO2/PIO3/PIO4/PIO5;否则串行Flash接口无效。

PIO复用说明

PIO模块可配置为GPIO,或作为前述通信接口。下表介绍所有PIO功能及复用情况。

| PIO # | 默认功能 | I/O | 说明 | 复用功能 |

|---|---|---|---|---|

| 0 | GPIO | I/O | - | SPI master MISO SPI flash D0 |

| 1 | GPIO | I/O | - | SPI master MOSI SPI flash D1 |

| 2 | GPIO | I/O | - | PWM0 UART2 RXD SPI flash WP |

| 3 | GPIO | I/O | - | PWM1 UART2 TXD SPI flash HOLD |

| 4 | GPIO | I/O | - | SPI master CLK SPI flash CLK |

| 5 | GPIO | I/O | - | SPI master CSN SPI flash CSN |

| 6 | GPIO | I/O | 启动时,该引脚受BOOT_MODE控制: UART1 TXD(当BOOT_MODE在启动 时为高) SPI slave MISO(当BOOT_MODE在 启动时为低) | UART1 TXD SPI slave MISO |

| 7 | GPIO | I/O | 启动时,该引脚受BOOT_MODE控制: UART1_RXD(当BOOT_MODE在启动 时为高) SPI slave MOSI(当BOOT_MODE在 启动时为低) | UART1 RXD SPI slave MOSI |

| 8 | GPIO | I/O | 启动时,该引脚受BOOT_MODE控制: I2C1 SCL(当BOOT_MODE在启动 时为高) SPI slave CLK(当BOOT_MODE在启 动时为低) | I2C1 SCL SPI slave CLK |

| 9 | GPIO | I/O | 启动时,该引脚受BOOT_MODE控制: I2C1 SDA(当BOOT_MODE在启动时 为高) SPI slave CSN(当BOOT_MODE在 启动时为低) | I2C1 SDA SPI slave CSN |

| 10 | GPIO | I/O | 通信接口选择引脚。选择通信接口位 于PIO6至PIO9。仅在启动时有效。 此引脚如果留空,则被上拉。 | PPS D_SEL 32.768 kHz clock out |

| 11 | GPIO | I/O | - | PPS EVENT UART1 RXD |

| 12 | GPIO | I/O | 引导程序模式选择引脚。 选择固件加载地址,外部/内部Flash 或者SPI接口。仅在启动时有效。 此引脚如果留空,则被上拉。 | BOOT MODE PPS RF_READY UART1 TXD |

| 13 | GPIO | I/O | ODO_DIR EVENT | |

| 14 | GPIO | I/O | - | ODO_CNT EVENT |

| 15 | GPIO | I/O | - | UART2 TXD LO1_DET |

| 16 | GPIO | I/O | - | UART2 RXD BLK LO2_DET |

| 17 | TMS | I/O | 调试接口 | ODO_DIR GPIO |

| 18 | TCK | I/O | 调试接口 | ODO_CNT GPIO |

I/O 复用部分修改详细,请咨询Unicore FAE。

时间管理单元

时间管理单元(TMU)管理基带中的所有时钟源,可以使用更精确的时钟来校准不太精确的时钟。

看门狗

UC6580x-00包含两个看门狗定时器,防止在软件陷入死锁时导致系统闭锁。在正常工作时,固件会在定时器发生溢出之前定期复位看门狗的内部计数器。

定时器计数器

定时器计数器有一个EVENT输入和一个PPS输出。

EVENT可以通过PIO11、PIO13或PIO14输入,但同一时间只能输入一个EVENT。EVENT输入为相对于GPS时间的时间戳外部事件。

EVENT功能默认不支持,如有需求请联系Unicore FAE。

PPS通过PIO11输出。PPS输出与GPS或UTC时间网格同步的脉冲序列,时间间隔可在很宽的频率范围内配置。

所有输入和输出信号均与接收机内部时钟频率同步,这使得输入和输出信号的固有最大量化误差达到±10 ns级别。

系统配置

电源供电方案

UC6580x-00支持2种供电方案:内部DC-DC模式和LDO模式。

DCDC_IN和VDD_IO采用相同电源供电。

V_BACK可单独供电,或者与DCDC_IN和VDD_IO采用相同电源供电。

TCXO供电使用LDO_X,电压可选择1.8 V或2.8 V1。

V_BACK供电电压需不低于主电VDD_IO或在V_BACK供电电压前加一个正向二极管防止VDD_IO给V_BACK倒灌电,同时V_BACK供电电压需保证为1.7 V ~ 3.6 V,建议选用小功率(正向电流mA级即可)、正向压降小(300 mV)、反向漏电流小(全温度范围内小于100 μA)的二极管。

如果不需要RTC和backup功能,则V_BACK需要连接VDD_IO。

DC-DC模式

在DC-DC模式下,主电(V_Main)接入DCDC_IN引脚,芯片的DC-DC模块输出DCDC_OUT给芯片其他部分提供电源供给,此时系统由内部DC-DC供电:

系统电源由DCDC_IN输入,DCDC_OUT输出经功率电感连接V_CORE输入引脚。

LDO模式

在LDO模式下,主电(V_Main)接入DCDC_IN引脚,DCDC_IN与DCDC_OUT短接,芯片的DCDC模块被旁路,直接由主电(V_Main)给芯片其他部分提供电源供给。此时:

DCDC_IN与DCDC_OUT短接在一起。

系统供电由 VDD_IO 输入,经过 LDO_EX 输出到 V_CORE, 由 LDO_EX 供电。

以上两种模式的具体设计方法请参考《UC6580x-00硬件参考设计和注意事项》。

1. LDO_X输出电压在芯片出厂时确定,无法通过固件更改。当前量产出货芯片输出为1.8V,如需2.8V输出,请提前联系原厂。 ↩

固件升级模式

UC6580x-00芯片通过D_SEL (PIO10) 和BOOT_MODE (PIO12) 引脚控制选择固件升级模式,分为三种情形:

Mode 1:通过UART1或I2C1升级,此时UART1引脚为PIO6/7,I2C1引脚为PIO8/PIO9。

Mode 2:通过UART1升级,此时UART1引脚为PIO11/12。

Mode 3:通过SPI slave升级,此时SPI slave引脚为PIO6至PIO9。

芯片启动时固件升级通信接口配置及升级模式说明参见下文。

BOOT_MODE仅在上电或RESETN被释放之前有效。RESETN被释放后,BOOT_MODE引脚可用作普通的PIO引脚。

固件升级启动时管脚功能配置

| Mode | D_SEL | BOOT_ MODE |

Boot Mode |

说明 | |||

| PIO 6/7 | PIO 8/9 | PIO 11/12 | |||||

| Mode 1 | 1 | X | UART1和 I2C1启动 |

UART1 | I2C1 | X | |

| Mode 2 | 0 | 1 | UART1 启动 |

X | X | UART1 | UART1从 PIO11/ PIO12 启动, 无I2C1启动 |

| Mode 3 | 0 | 0 | SPI slave 启动 |

SPI slave | SPI slave | X | |

这三种固件升级模式的启动过程如下:

步骤1 CPU检测接口的固件升级请求。

Mode 1升级模式

| If | Then |

|---|---|

| CPU在上电或复位后的40 ms内检测到UART1的固件升级请求 | CPU开始自适应波特率并升级固件,升级完成后运行 |

| CPU在上电或复位后的40 ms内检测到I2C1的固件升级请求 | CPU开始自适应I2C时钟并升级固件,升级完成后运行 |

| CPU在上电或复位后的40 ms内同时检测到UART1和I2C1的固件升级请求 | 优先初始化已识别波特率的接口,读取该接口的升级请求,升级完成后运行 |

| CPU在上电或复位后的40 ms内未检测到UART1或I2C1的固件升级请求 | 进行步骤2 |

Mode 2升级模式

| If | Then |

|---|---|

| CPU在上电或复位后的40 ms内检测到UART1的固件升级请求 | CPU开始自适应波特率并升级固件,升级完成后运行 |

| CPU在上电或复位后的40 ms内未检测到UART1的升级请求 | 进行步骤2 |

Mode 3升级模式

| If | Then |

|---|---|

| CPU在上电或复位后的40 ms内检测到SPI slave接口的固件升级请求 | CPU升级固件,升级完成后运行 |

| CPU在上电或复位后的40 ms内未检测到SPI slave接口的升级请求 | 进行步骤2 |

步骤2 CPU顺序检查封装内嵌Flash以及外部Flash。

CPU检测Flash

| If | Then |

|---|---|

| CPU检测到封装内嵌Flash中的固件 | 读取内嵌Flash中的固件并运行 |

| CPU检测到封装内嵌Flash中无固件 | CPU尝试读取外部Flash中的固件,并运行。 |

电气特性指标

本章介绍UC6580系列芯片的电气特性指标。

其中,UC6580A-00的工作温度为-40℃~105℃,UC6580I-00的工作温度为-40℃~85℃。

以上温度条件适用于本章所有电气特性指标。

直流电气特性指标

最大绝对额定值

| 符号 | 参数 | 最小值 | 最大值 | 单位 |

|---|---|---|---|---|

| DCDC_IN | 内部DC/DC转换器输入电压 | -0.2 | 3.6 | V |

| DCDC_OUT | 内部DC/DC转换器的输出电压, 外接电感及滤波电容,提供1.0V供电 建议电感值1uH,建议电容值10uF。 | -0.2 | 1.05 | V |

| VDD_IO | I/O,LDO_X和flash输入电压 | -0.2 | 3.6 | V |

| V_BACK | 备份域输入电源电压 | -0.2 | 3.6 | V |

| TCXO_IN | TCXO_IN上输入电压 | -0.6 | 2.9 | V |

| RTC_I | RTC_I上输入电压 | -0.2 | 1.98 | V |

| Vidig | PIO上输入电压 | -0.2 | 3.6 | V |

| Prfin | LNA_IN上RF输入功率 | +15 | dBm | |

| Ptot | 总功率 | 360(常温) | mW | |

| Tjun | 结温 | -40 | +125 | °C |

| Ts | 储存温度 | -50 | +150 | °C |

所有输入电压,纹波均不能超过50 mV。

推荐工作条件

| 符号 | 参数 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| DCDC_IN | 内部DC/DC转换器输入电压 | 1.7 | 3.3 | 3.6 | V |

| VDD_IO | I/O,LDO_X 和flash输入电压 | 1.7 | 3.3 | 3.6 | V |

| V_BACK | 备份域输入电源电压 | 1.7 | 3.3 | 3.6 | V |

PIO电气特性指标

| 符号 | 参数 | 条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|---|

| Ileak | 输入管脚 漏电 | 5 | μA | |||

| Vil | 允许输入 的低电平 幅度 | 0.2×VDD_IO | V | |||

| Vih | 允许输入 的高电平 幅度 | 0.8×VDD_IO | V | |||

| Vol | 输出低电 平幅度 | Iout = -5mA | 0.4 | V | ||

| Voh | 输出高电 平幅度 | Iout = 5mA | VDD_IO-0.55 | V | ||

| Rpu | 上拉电阻 | 200 | 260 | 320 | kΩ | |

| Cap_DIG_IN | 数字IO输 入阻抗 | 0.7 | pF |

PIO输出方式为推挽。

模拟电气特性指标

模拟电气特性指标1

| 符号 | 参数 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| LDO_X1 | LDO_X输出电压 (1.8 V TCXO) | 1.75 | 1.8 | 1.95 | V |

| LDO_X输出电压 (2.8 V/2.9 V TCXO) | 2.75 | 2.8 | 2.95 | V | |

| LDO_RET | LDO_RET输出电压 (VDD_IO 有电, V_BACK 有电) | 0.85 | 0.9 | 0.95 | V |

| LDO_RET输出电压 (VDD_IO 无电, V_BACK 有电) | 0.55 | 0.65 | 0.75 | V | |

| LDO_C | LDO_C 输出电压 | 0.85 | 0.9 | 0.95 | V |

| LDO_EX | LDO_EX输出电压 | 0.95 | 1.0 | 1.05 | V |

| V_DET2 | 天线检测输入 | 2.7 | 3.3 | 3.6 | V |

| VDD_ANT3 | 天线供电输出 | 2.7 | 3.3 | 3.6 | V |

| RTC_I | 32.768 kHz晶体或 数字波形输入 | 1.98 | V | ||

| RTC_O | 32.768 kHz时钟输出 | 1.98 | V | ||

| DCDC_OUT | 内部DC/DC转换器的输出电压, 外接电感及滤波电容,提供1.0V供电。 建议电感值1uH,建议电容值10uF。 | 0.95 | 1.0 | 1.05 | V |

| TCXO_IN_Vpp | TCXO输入峰-峰电压 | 0.5 | 0.6 | 1.4 | Vpp |

1. LDO_X输出电压在芯片出厂时确定,无法通过固件更改。当前量产出货芯片输出为1.8V,如需2.8V输出,请提前联系原厂。 ↩

2. 暂不支持天线检测 ↩

3. VDD_ANT输出电压为V_DET – (天线电流) × (10 Ω)。 ↩

模拟电气特性指标2 - RTC指标要求

| 符号 | 参数 | 条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|---|

| RTC_Fxtal | RTC晶振共振 频率 | 32768 | Hz | |||

| RTC_T_start | RTC启动时间 | 0.2 | 1 | 2 | s | |

| RTC_CL | RTC负载电容 | ESR = 80 kΩ | 12.5 | pF | ||

| RTC_Vil | RTC低电平输 入电压 | 共用RTC振荡 器输入 | 0.0 | 0.2 | V | |

| RTC_Vih | RTC高电平输 入电压 | 共用RTC振荡 器输入 | 0.9 | 1.98 | V |

RF电气特性指标

| 符号 | 参数 | 条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|---|

| L1_IN | 接收机输 入频率 | 1559.098 | 1575.42 | 1606 | MHz | |

| L5_IN | 接收机输 入频率 | 1166.45 | 1176.45 | 1217.14 | MHz | |

| LNA_IN | LNA输入 阻抗 | 需要匹配 器件和 隔直电容 | 50 | Ω | ||

| LNA_S11 | LNA输入 回波损耗 | 50 Ω环境 | -10 | dB | ||

| NFtot | 接收机级 联噪声系 数 | 50 Ω环境 | 5 | dB | ||

| Ext_Gain | 外部LNA 增益 | 50 Ω环境 | 15 | 17 | 60* | dB |

| TCXO_Freq | TCXO 频 率 | 0.5 ppm | 26 | MHz |

*. 外部LNA增益在该范围时,系统CN0波动1 dB。 ↩

机械尺寸

UC6580A-00 (QFN40车规)

UC6580I-00 (QFN40工规)

焊接要求

焊接要求

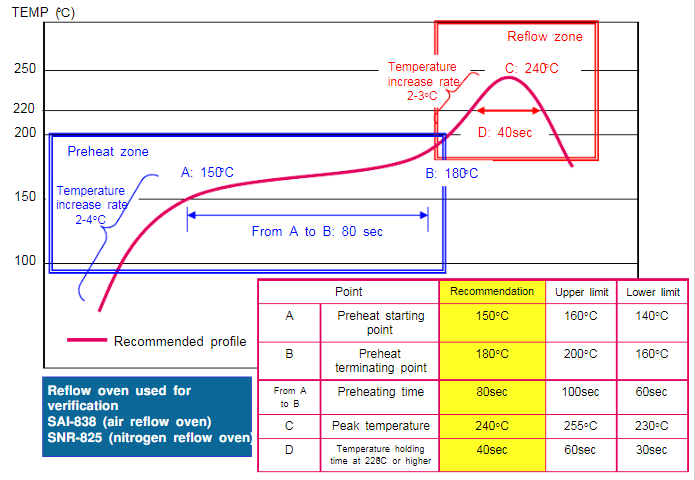

回流焊温度曲线建议采用如下图所示(锡膏建议使用M705-GRN360)。

产品外观及包装

外观

UC6580A-00(QFN40车规) |

UC6580I-00(QFN40工规) |

标识

| 型号 | 说明 |

|---|---|

| UC6580A-00 | 级别-车规级(Automotive) |

| UC6580I-00 | 级别-工规级(Industrial) |

湿度敏感等级

UC6580A和UC6580I的湿度敏感等级如下表所示,与湿敏等级相关的包装及操作注意事项参照标准 IPC/JEDEC J-STD-033。了解更多信息,可访问JEDEC网站。

| 型号 | 湿度敏感等级 |

|---|---|

| UC6580A-00 | MSL 1 |

| UC6580I-00 | MSL 3 |

订货信息

| 型号 | 封装 | 内置Flash | 工作温度 | 等级 | 包装 |

|---|---|---|---|---|---|

| UC6580A-00 | QFN40 5 mm × 5 mm × 0.85mm | Yes | -40 °C ~ 105 °C | 车规级 | 卷带包装, 每卷3000片 |

| UC6580I-00 | QFN40 5 mm × 5 mm × 0.85mm | Yes | -40 °C ~ 85 °C | 工规级 | 卷带包装, 每卷3000片 |